Асанова С.М., Айдарова А.Р., Мырзаканова Р.А.

# ВЫЧИСЛИТЕЛЬНЫЕ СЕТИ ПЕТРИ ДЛЯ МОДЕЛИРОВАНИЯ СИСТЕМЫ ДИСТАНЦИОННОЙ ДИАГНОСТИКИ ОБРЫВА ПРОВОДА ВЛ 6-35 кВ

S.M. Asanova, A.R. Aidarova, R.A. Mirzakanova

## COMPUTATIONAL PETRI NETS FOR MODELING A SYSTEM OF REMOTE DIAGNOSIS WIRE BREAK 6-35 KV OTL

УДК.: 004.72:001.891.54:621.316.962

С помощью аппарата вычислительных сетей Петри разработан самоорганизующийся, многокомпонентный, структурно-подобный вычислительный алгоритм для проектирования системы дистанционной и оперативной диагностики обрыва провода воздушных линий распределительных электрических сетей.

By means of the network apparatusPetry, self organized, multicomponent ,structure like network algorithm was worked out for the design system of the distant and operation diagnostics of the disconnection of the overhead wires that distribute the electric network.

Введение. В работе [1] предложен способ дистанционного и оперативного обнаружения обрыва провода воздушных линий (ВЛ) распределительных электрических сетей (РЭС) 6-35 кВ. В этом способе предполагается, что электрическая сеть выполнена с использованием многофункционального провода (МП), где одна из токопроводящих жил изолирована от остальных, конструкция которого запатентована.

Описанные в работе [1] алгоритмы расчета желаемого распределения токов по информационным проводам участков сети и расчета настраисопротивлений имеют классическую структуру организации вычислительных процессов, где с трудом проглядывается структура самой проектируемой системы, что приводит к определенным трудностям при их понимании, реализации на ЭВМ и результатов. Указанные анализе полученных трудности многократно повышаются при увеличении размерности и усложнении структуры проектируемой системы. Удобным средством для построения структурноподобных вычислительных алгоритмов, является аппарат вычислительных сетей Петри (ВСП) [2]. Далее описывается ВСП, реализующие структурно подобный вычислительный алгоритм проектирования распределительных электрических обнаруживающих обрывы проводов систем, участков двухпроводных РЭС.

Постановка задачи и схема ее решения описана в работе [1]. С целью использования аппарата ВСП

при проектировании распределительных электричессистем, представим процедуры анализа топологии сети, расчета желаемого распределения токов по информационным проводам участков сети и расчета настраиваемых сопротивлений цепи для получения желаемого распределения токов, как управляемый дискретный динамический процесс движения информационных маркеров на графах сети и их соответствующего преобразования. ВС $\Pi_{\Pi P}$ реализующий процесс проектирования, состоит из  $BC\Pi_I$  и  $BC\Pi_{II}$ , взаимосвязанных через соответствующие позиции, где ВСП предназначена для реализации вычислительного алгоритма анализа топологии и расчета желаемого распределения токов по информационным проводам путем управляемого движения и преобразования информационных маркеров, начиная с конечных узлов (вершин) в направлении узла питания (начальной вершины) графа сети, а ВСП<sub>ІІ</sub> - алгоритма расчета настраисопротивлений цепи для получения желаемого распределения токов путем движения и преобразования информационных маркеров, начиная с узла питания, в направлении конечных узлов графа сети.

Функциональная схема  $BC\Pi_I$  имеет двухуровневую структуру и является объединением схем вычислительных блоков нижнего  $BC\Pi_{\Gamma p}$  и верхнего  $BC\Pi_{y_{\Pi p}}$  уровней:

$$BC\Pi_{I} = BC\Pi_{\Gamma p} \bigcup BC\Pi_{y_{\Pi p}} \tag{1}$$

При функционировании ВСП $_{\Gamma p}$  формируется многоуровневая иерархическая схема графа электрической цепи информационных проводов (см. [1] рис. 5 и 6) путем разбиения множества узлов (вершин) исходного графа на уровни иерархии и, по мере такого разбиения, производится, под управлением ВСП $_{\rm Упр}$ , расчет желаемого распределения токов по информационным проводам. ВСП $_{\Gamma p}$  является объединением схем (графов) вычислительных блоков и модулей, показанных на рис. 1:

$$BC\Pi_{\Gamma p} = (\bigcup_{i_2 \in L_0} BC\Pi_{i_2}^0) \cup (\bigcup_{i_2 \in (L \setminus L_0) \setminus \{0\}} BC\Pi_{i_2}^s) \cup (\bigcup_{i_1 \in L \setminus L_0} BC\Pi_{\Gamma(i_1)})$$

, (1.1)

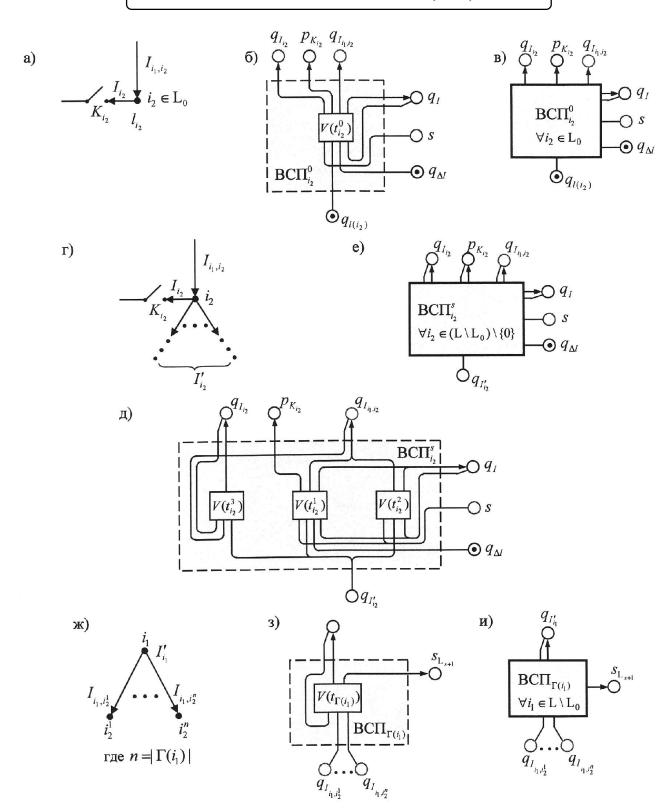

Рис. 1. ВСП узлов (вершин) графа электрической цепи информационных проводов

где  $\mathrm{BC\Pi}_{i_2}^0$ ,  $\forall i_2 \in \mathrm{L}_0$  - вычислительный блок конечного узла  $i_2 \in \mathrm{L}_0$ , предназначенный для вычисления токов  $I_{i_1,i_2}$ ,  $I_{i_2}$  и состояния условного ключа  $K_{i_2}$  для этого конечного узла; каждый блок  $\mathrm{BC\Pi}_{i_2}^0$  состоит из одного вычислительного модуля  $V(t_{i_2}^0)$  перехода  $t_{i_2}^0$  (см. рис. 1,  $a,\delta,\epsilon$ );  $\mathrm{BC\Pi}_{i_2}^0$ ,  $\forall i_2 \in (\mathrm{L}\setminus \mathrm{L}_0)\setminus\{0\}$  - вычислительный блок промежуточного узла  $i_2 \in (\mathrm{L}\setminus \mathrm{L}_0)\setminus\{0\}$ , предназначенный для вычисления токов  $I_{i_1,i_2}$ ,  $I_{i_2}$  и состояния условного ключа  $K_{i_2}$  для этого промежуточного узла; каждый блок  $\mathrm{BC\Pi}_{i_2}^0$  состоит из трех взаимосвязанных вычислительных модулей  $V(t_{i_2}^1)$ ,  $V(t_{i_2}^2)$ ,  $V(t_{i_2}^3)$  переходов соответственно  $t_{i_2}^1$ ,  $t_{i_2}^2$ ,  $t_{i_2}^3$  (см. рис. 1,  $\epsilon,\delta,\epsilon$ );  $\mathrm{BC\Pi}_{\Gamma(i_1)}$ ,  $\forall i_1 \in \mathrm{L}\setminus \mathrm{L}_0$  - вычислительный блок, предназначенный для вычисления суммарного тока  $I'_{i_1}$ , вытекающего из узла  $i_1$  по множеству ориентированных ветвей, начальными вершинами которых является  $i_1$ , а конечными - вершины из множества  $\Gamma(i_1)$ , и участвующий в разбиении множества узлов (вершин) исходного графа сети на уровни иерархии, т.е. в формировании множества  $\mathrm{L}_{s+1}$  для определенного (s+1)-го уровня, где  $s=0,1,2,\ldots$ ; каждый блок  $\mathrm{BC\Pi}_{\Gamma(i_1)}$  состоит из одного вычислительного модуля  $V(t_{\Gamma(i_1)})$  перехода  $t_{\Gamma(i_1)}$  (см. рис. 1,  $\kappa,s,u$ ). Функциональная схема  $\mathrm{BC\Pi}_{\mathsf{упр}}$  в виде взаимосвязанных вычислительных модулей  $V(t_0^0)$ , ...,  $V(t_5^0)$ , переходов, соответственно,  $t_0^0$ , ...,  $t_5^0$ , показана на рис. 2.

В схеме ВСП<sub>1</sub> предусмотрены позиции  $\{q_{l(i)} \mid i \in L_0\}$  ,  $q_{\Delta l}$  ,  $s_0$  ,  $q_U$  , для хранения исходных данных решаемой задачи. При наличии в них исходных данных (информационных маркеров), их состояние:

$$\mu(q_{I(i)}) = l(i), \ \forall i \in L_0; \ \mu(q_{\Lambda I}) = \Delta I; \ \mu(s_0) = q_{I_0}; \ \mu(q_{II}) = U_0.$$

(2)

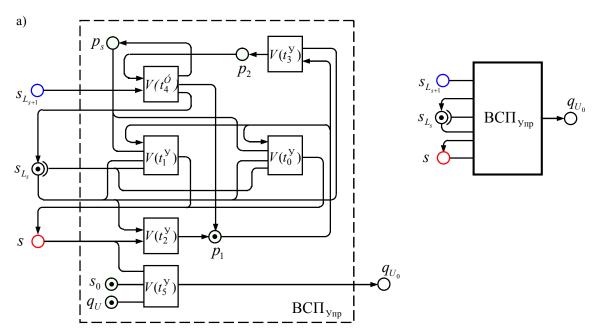

**Рис. 2.** ВСП для управления последовательностью срабатывания ВСП узлов (вершин) графа электрической цепи информационных проводов

Состояние процесса функционирования ВСП характеризуется состоянием позиций

$$\begin{aligned} q_{I_{i_1,i_2}}, \ \forall (i_1, i_2) \in \Gamma, \ q_{I_i}, \ p_{K_i}, \ \forall i \in L \setminus \{0\}, \\ q_{I_i'}, \ \forall i \in L \setminus L_0, \ q_{I}, \ s_{L_{s+1}}, \ s_{L_s}, \ s, \ p_1, \ p_2, \ p_s \end{aligned} \tag{3}$$

При наличии в них информационных маркеров, их состояние:

$$\mu(q_{I_{i_1,i_2}}) = I_{i_1,i_2}, \ \forall (i_1, i_2) \in \Gamma;$$

(4)

$$\mu(q_{I_i}) = I_i, \quad \mu(p_{K_i}) = K_i = 1, \quad \forall i \in L \setminus \{0\};$$

(5)

$$\mu(q_I) = I_i', \quad \forall i \in L \setminus L_0; \quad \mu(q_I) = I; \tag{6}$$

$$\mu(s_{L_{s+1}}) \subseteq \{q_{I'_i} | i \in L_{s+1}\};$$

(7)

$$\mu(s_{L_s}) \subseteq \begin{cases} \{q_{l(i)} \mid i \in L_0\}, & \textit{при рассмотрении } s = 0 - \textit{го} \\ & \textit{уровня иерархии,} \\ \{q_{I_i'} \mid i \in L_s\}, & \textit{при рассмотрении } s > 0 - \textit{го} \\ & \textit{уровня иерархии,} \end{cases}$$

(8)

$$\mu(s) \in \mu(s_{L_s}), \quad \mu(p_1) = \mu(p_2) = 1, \quad \mu(p_s) = 1, \, 2, \, 3, \dots$$

(9)

Здесь: позиции  $q_I$ , s,  $q_{\Delta I}$  являются общими для вычислительных блоков  $\mathrm{BC\Pi}_i^0$ ,  $\forall i \in \mathrm{L}_0$  и  $\mathrm{BC\Pi}_i^s$ ,  $\forall i \in (\mathrm{L} \setminus \mathrm{L}_0) \setminus \{0\}$  (см. рис. 1, a-e), а позиция  $s_{\mathrm{L}_{s+1}}$  - общим для вычислительных блоков  $\mathrm{BC\Pi}_{\Gamma(i)}$ ,  $\forall i \in \mathrm{L} \setminus \mathrm{L}_0$  (см. рис. 1, x-u); через позиции  $s_{\mathrm{L}_{s+1}}$ , s и указателя &  $s_{\mathrm{L}_s}$  осуществляется обмен информацией между вычислительными блоками нижнего  $\mathrm{BC\Pi}_{\Gamma p}$  и верхнего  $\mathrm{BC\Pi}_{\mathrm{Упр}}$  уровнями.

По завершении функционирования  $\mathrm{BC\Pi_{I}}$ , вычислительный блок верхнего уровня  $\mathrm{BC\Pi_{ynp}}$  преобразует состояние позиции  $q_{U_0}$  из  $\mu(q_{U_0})=0$  в  $\mu(q_{U_0})=U_0$ , в результате чего запускается  $\mathrm{BC\Pi_{II}}$  для реализации вычислительного алгоритма расчета настраиваемых сопротивлений электрической цепи информационных проводов.

**Вычислительный алгоритм, реализуемый при функционировании ВСП**<sub>I</sub>. Позиции, необходимые для хранения информационных маркеров при функционировании ВСП<sub>I</sub>, определены в (3)-(8). Исходными данными для функционирования ВСП<sub>I</sub> являются состояния позиций из (2). Начальное состояние позиций  $s_{\rm L_s}$ ,  $p_{\rm 1}$  из набора (3):  $\mu(s_{\rm L_s}) = \{q_{l(i)} | i \in {\rm L_0}\}$ ;  $\mu(p_{\rm 1}) = 1$ . Остальные же позиции из данного набора (3) пустые, т.е. в них отсутствуют маркеры. Маркированные позиции на рис. 1 и 2 изображены как кружочки с фишками. Вычислительный алгоритм, заложенный в ВСП<sub>I</sub> (1), включает вычислительные процедуры, реализуемые при функционировании ВСП<sub>упр</sub> и ВСП<sub>гр</sub>, взаимосвязанных через позиции  $s_{\rm L_{s,1}}$ , s и указатель &  $s_{\rm L_s}$ .

**1.** Процедуры, реализуемые при функционировании ВСП $_{y_{mp}}$  (см. рис. 1):

а) при  $(\mu(p_s)=0)$  &  $(\mu(p_1)=1)$  &  $(\mu(s_{L_s})\neq$ ""), переход  $t_0^{\circ}$  - активный. Срабатывает  $V(t_0^{\circ})$ , в результате чего

$$\mu(s) = q_{l(i)} \in \mu(s_{L_s})$$

такое, что  $\mu(q_{l(i)}) = \max \mu(\&s_{L_s}) = \max_{x \in \mu(s_{L_s})} \mu(x), \quad \mu(p_1) = 0;$

(10)

б) при  $(\mu(p_s) > 0)$  &  $(\mu(p_1) = 1)$  &  $(\mu(s_{L_s}) \neq "")$ , переход  $t_1^{\circ}$  - активный. Срабатывает  $V(t_1^{\circ})$ , в результате чего

$$\mu(s) = q_{I_i'} \in \mu(s_{L_s})$$

такое, что  $\mu(q_{I_i'}) = \min \mu(\&s_{L_s}) =$

$$= \min_{x \in \mu(s_{L_s})} \mu(x), \ \mu(p_1) = 0;$$

(11)

в) при  $\mu(s) \neq$ " ", переход  $t_2^{\circ}$  - активный. Срабатывает  $V(t_2^{\circ})$ , в результате чего

$$\mu'(s_{L_s}) = \mu(s_{L_s}) \setminus \mu(s), \quad \mu(s) = "", \quad \mu(p_1) = 1;$$

(12)

г) при

$$(\mu(p_1)=1)$$

&  $(\mu(s_{\mathbf{L}_s})=$ ""), переход  $t_3^{\circ}$  - активный. Срабатывает  $V(t_3^{\circ})$ , в результате чего

$$\mu(p_2)=1, \quad \mu(p_1)=0 \,; \tag{13}$$

д) при  $(\mu(p_2)=1)$  &  $(\mu(s_{\mathsf{L}_{\mathsf{cul}}}) \neq "")$  , переход  $t_4^{\circ}$  - активный. Срабатывает  $V(t_4^{\circ})$  , в результате чего

$$\mu(s_{L_{s,1}}) = \mu(s_{L_{s,1}}), \quad \mu(s_{L_{s,1}}) = "", \quad \mu(p_1) = 1, \quad \mu(p_2) = 0;$$

(14)

е) при  $\mu(s)=\mu(s_0)$  , переход  $t_5^{\circ}$  - активный. Срабатывает  $V(t_5^{\circ})$  , в результате чего

$$\mu(q_{U_0}) = \mu(q_U). \tag{15}$$

ВСП<sub>Упр</sub>, управляя состоянием  $\mu(s)$  позиции s (10), (11) на основе топологической информации  $\mu(s_{\rm L_{s+1}})$  (14), (17), поступающей в позицию  $s_{\rm L_{s+1}}$  от ВСП $_{\rm \Gamma p}$ , управляет вычислительным процессом, протекающим при функционировании ВСП $_{\rm \Gamma p}$ .

**2.**Процедуры, реализуемые при функционировании ВСП $_{\Gamma_p}(11)$ , состоящей из вычислительных блоков ВСП $_{i_2}^0$ ,  $\forall i_2 \in L_0$ , ВСП $_{i_2}^s$ ,  $\forall i_2 \in (L \setminus L_0) \setminus \{0\}$  и ВСП $_{\Gamma(i_1)}$ ,  $\forall i_1 \in L \setminus L_0$  (см. рис.1):

а) при  $\mu(s) = \mid (q_{l(i_2)})$  , переход  $t_{i_2}^0$  - активный. Срабатывает  $V(t_{i_2}^0)$  , в результате чего (см. рис. 1, a, $\delta$ ,s)

$$\mu(q_{I_{i_1,i_2}}) = \mu(q_{I_{i_2}}) = \mu(q_I) + \mu(q_{\Delta I}), \tag{16}$$

$$\mu'(q_I) = \mu(q_I) + \mu(q_{\Delta I}), \quad \mu(p_{K_{i_0}}) = 1;$$

(17)

б) при  $\mu(s) = |(q_{I_{i_2}})|$  начинает функционировать ВСП $_{i_2}^s$ , состоящая из вычислительных модулей  $V(t_{i_1}^1),\ V(t_{i_2}^2),\ V(t_{i_3}^3)$  (см. рис. 1,  $\varepsilon,\partial,e$ ), т.е.

чего

- при  $(\mu(s) = |(q_{I'_{i_2}}))$  &  $(\mu(q_{I'_{i_2}}) \le \mu(q_I))$ , переход  $t^1_{i_2}$  - активный. Срабатывает  $V(t^1_{i_2})$ , в результате

$$\mu(q_{I_{n,i}}) = \mu(q_I) + \mu(q_{\Delta I}),$$

(18)

$$\mu'(q_I) = \mu(q_I) + \mu(q_{\Delta I}),$$

(19)

$$\mu(p_{K_{i_2}}) = 1; (20)$$

- при  $(\mu(s) = |(q_{I_{i_2}}))$  &  $(\mu(q_{I_{i_2}}) > \mu(q_I))$ , переход  $t_{i_2}^2$  - активный. Срабатывает  $V(t_{i_2}^2)$ , в результате чего

$$\mu(q_{I_{i_1,i_2}}) = \mu(q_{I'_{i_2}}), \tag{21}$$

$$\mu(q_I) = \mu(q_{I_{l_2}}); \tag{22}$$

- при  $(\mu(q_{I_{i_1,i_2}}) > 0)$  &  $(\mu(q_{I_{i_2}}) = 0)$  , переход  $t_{i_2}^3$  - активный. Срабатывает  $V(t_{i_2}^3)$  , в результате чего  $\mu(q_{I_{i_2}}) = \mu(q_{I_{i_1,i_2}}) - \mu(q_{I'_{i_2}}) \,; \tag{23}$

в) при  $(\mu(q_{I_{i_1,i_2}}) > 0$ ,  $\forall i_2 \in \Gamma(i_1)$ ) &  $(\mu(q_{I'_{i_1}}) = 0)$ , переход  $t_{\Gamma(i_1)}$  - активный. Срабатывает  $V(t_{\Gamma(i_1)})$ , в результате чего (см. рис. 1, ж,з,и)

$$\mu(q_{I'_{i_1}}) = \sum_{i_2 \in \Gamma(i_1)} \mu(q_{I_{i_1,i_2}}), \qquad (24)$$

$$\mu'(s_{L_{s+1}}) = \mu(s_{L_{s+1}}) \circ |(q_{I'_{h}}). \tag{25}$$

Вычислительные модули  $V(t_{\Gamma(i_1)})$ ,  $\forall i_1 \in L \setminus L_0$  участвуют в формировании топологической информации  $\mu(s_{L_{s+1}})$  (25), (27).

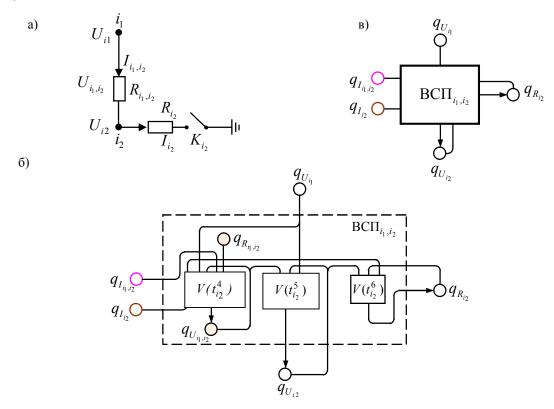

**Функциональная схема ВСП**п для расчета настраиваемых сопротивлений цепи информационных проводов.

По окончании работы ВСП $_{\rm I}$  начинает функционировать ВСП $_{\rm II}$ . Условием начала ее функционирования является наличие информационного маркера в позиции  $q_{U_0}$ , т.е. информации о напряжении в узле питания  $\mu(q_{U_0}) = \mu(q_U) = U_0$  (15), (2). ВСП $_{\rm II}$  является объединением схем (графов) вычислительных блоков и модулей, показанных на рис. 3:

$$BC\Pi_{II} = \bigcup_{(i_1, i_2) \in \Gamma} BC\Pi_{i_1, i_2} , \qquad (26)$$

где  $\mathrm{BC\Pi}_{i_1,i_2}, \ \forall (i_1,i_2) \in \Gamma$  - вычислительный блок ориентированной ветви  $(i_1,i_2) \in \Gamma$ , предназначенный для вычисления напряжения  $U_{i_2}$  и настраиваемого сопротивления  $R_{i_2}$ ; каждый блок  $\mathrm{BC\Pi}_{i_1,i_2}$  состоит из трех взаимосвязанных вычислительных модулей  $V(t_{i_2}^4),\ V(t_{i_2}^5),\ V(t_{i_2}^6)$  переходов, соответственно,  $t_{i_2}^4,\ t_{i_2}^5,\ t_{i_2}^6$  (см. рис. 3).

Рис. 3. ВСП ветвей (дуг) графа электрической сети информационных проводов

В схеме ВСП<sub>ІІ</sub> предусмотрены позиции  $\{q_{R_{i_1,i_2}} \mid (i_1, i_2) \in \Gamma\}$  для хранения исходных данных:

$$\mu(q_{R_{i_1,i_2}}) = R_{i_1,i_2}, \ \forall (i_1, i_2) \in \Gamma.$$

(27)

Позиции  $\{q_{I_{i1,i2}} \mid (i_1,i_2) \in \Gamma\}$ ,  $\{q_{I_i} \mid i \in L \setminus \{0\}\}$ ,  $q_{U_0}$  предназначены для хранения выходной информации ВСП<sub>I</sub> (24), (25), являющейся одновременно входной для ВСП<sub>II</sub>:

$$\mu(q_{I_{i_1,i_2}}) = I_{i_1,i_2}, \ \forall (i_1, i_2) \in \Gamma; \ \mu(q_i) = I_i, \ \forall i \in L \setminus \{0\}; \ \mu(q_{U_0}) = U_0.$$

(28)

Состояние процесса функционирования ВСП $_{\rm II}$  характеризуется состоянием позиций  $\{q_{U_{0,1,2}} \mid (i_1,i_2) \in \Gamma\}$ ,  $\{q_{U_i} \mid i \in L \setminus \{0\}\}$ ,  $\{q_{R_i} \mid i \in L \setminus \{0\}\}$ .

При наличии в них информационных маркеров, их состояние:

$$\mu(q_{U_{0,1}}) = U_{i_1,i_2}, \ \forall (i_1, i_2) \in \Gamma;$$

(29)

$$\mu(q_{U_i}) = U_i, \ \forall i \in L \setminus \{0\}; \tag{30}$$

$$\mu(q_R) = R_i, \forall i \in L \setminus \{0\}. \tag{31}$$

Вычислительный алгоритм, реализуемый при функционировании ВСП $_{\rm II}$ . Позиции, необходимые для хранения информационных маркеров при функционировании ВСП $_{\rm II}$ , определены в (29)-(31), а в (28) – определена входная информация, поступившая от ВСП $_{\rm II}$ . Исходными данными для функционирования ВСП являются состояния позиций из (27). Начальные состояния позиций из (29)-(31) — пустые, т.е. в них отсутствуют маркеры. Вычислительный алгоритм, заложенный в ВСП $_{\rm II}$  (26), включает следующие вычислительные процедуры:

- а) при  $(\mu(q_{U_{i1}}) > 0)$  &  $(\mu(q_{U_{i1,i2}}) = 0)$ , переход  $t_{i_2}^4$  активный. Срабатывает  $V(t_{i_2}^4)$ , в результате чего  $\mu(q_{U_{i1,i2}}) = \mu(q_{R_{i1,i2}}) * \mu(q_{I_{i1,i2}})$ ;

- б) при  $(\mu(q_{U_{i_1,i_2}})>0)$  &  $(\mu(q_{U_{i_2}})=0)$ , переход  $t_{i_2}^5$  активный. Срабатывает  $V(t_{i_2}^5)$ , в результате чего  $\mu(q_{U_{i_2}})=\mu(q_{U_{i_1}})-\mu(q_{U_{i_2}})$ ;

- в) при  $(\mu(q_{U_{i_2}}) > 0)$  &  $(\mu(q_{I_{i_2}}) > 0)$  &  $(\mu(q_{R_{i_2}}) = 0)$  , переход  $t_{i_2}^6$  активный. Срабатывает  $V(t_{i_2}^6)$  , в результате чего  $\mu(q_{R_{i_2}}) = \mu(q_{U_{i_2}})/\mu(q_{I_{i_2}})$  .

**Заключение.** Таким образом, вычислительные сети Петри использованы для построения самоорганизующихся, многокомпонентных, вычислительных алгоритмов анализа топологии и проектирования системы дистанционной и оперативной диагностики обрыва провода ВЛ РЭС 6-35 Кв.

#### Литература

- 1. Асанова С.М., Айдарова А.Р., Калматов У.А. Проектирование и моделирование системы дистанционной диагностики обрыва провода ВЛ 6-35 кВ. Настоящий сборник.

- 2. Асанова С.М. Моделирующие возможности вычислительных сетей Петри и их использование в решении задач электроэнергетики. Проблемы управления и автоматики: докл. II межд. конф. Кн2. НАН КР Бишкек: ИАИТ, 2007. С. 223-227.

Рецензент: к.т.н. Сатаркулов К.А.